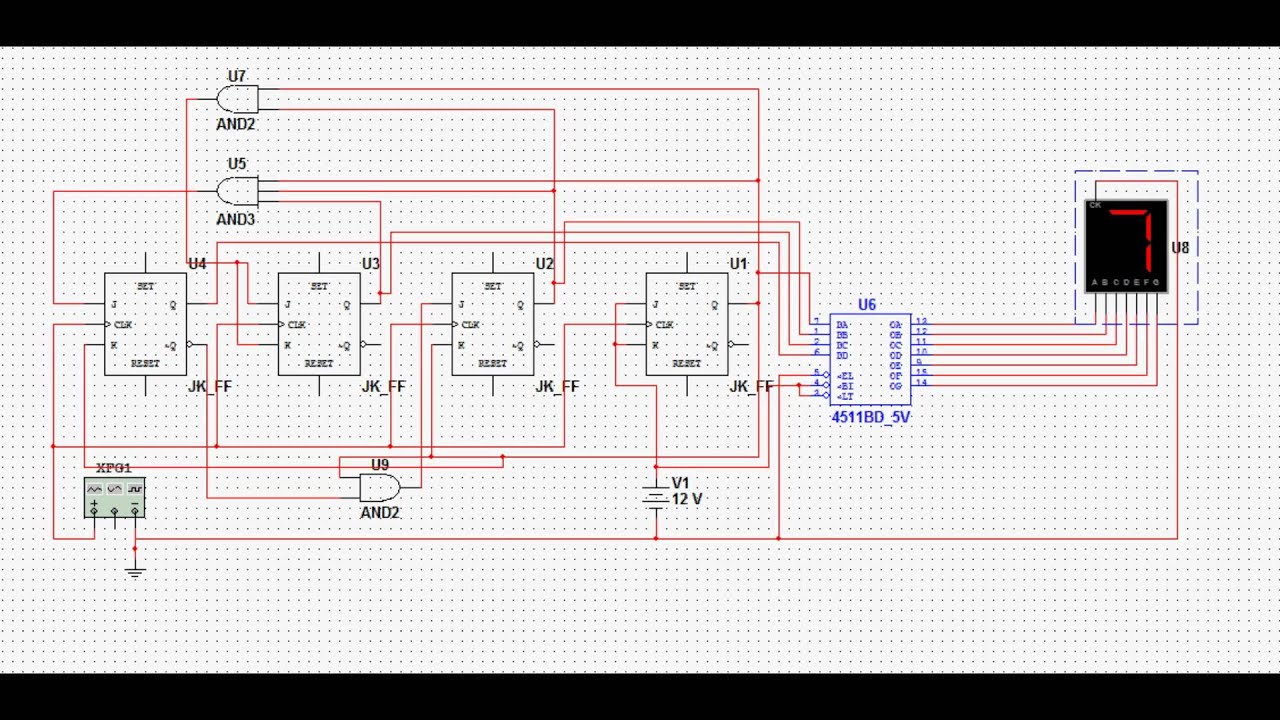

Preview of Counter to 7 Segment Display with JK Flip-flops and Logic Gates. Next, a process to derive the clock pulse: process(Clk)Ĭlk_pulse Clk, becomes Clk => Clk_pulse. This is a 3 bit Ripper counter using D flip flops and it is counting from 0,1. Note that this is simulation-only code, so you can use initial values however you like. We can easily shorten the clock pulse width to get rid of these oscillations by adding a new 'pulse' signal, derived from the clock: signal Clk_pulse : std_logic := '0' WebThe flip flop is a basic building block of sequential logic circuits. You can now see the oscillations that result from too long a clock pulse in the simulation waveform: J-K Flip Flop 3-Bit Counter - Multisim Live U3L6.3 3 Bit synchronous Up/Down Counter using JK. Notice how the clock signal in this example has a duty cycle less than 50. To reset Q in a J-K flip flop we must set J0 and K1. To start with, the conventional way to design a JK flip flop in VHDL would look like this: signal Q_s : std_logic The first flip-flop (the one with the Q 0 output), has a positive-edge triggered clock input, so it toggles with each rising edge of the clock signal.

0 kommentar(er)

0 kommentar(er)